# ESTUDO DO COMPORTAMNETO DO INVERSOR CMOS EM DIFERENTES TEMPERATURAS

Carolina de Fátima Garcez Sanavio<sup>1</sup>, Paula Ghedini Der Agopian<sup>2</sup>

1,2 Centro Universitário FEI

Sanavio.ca@hotmail.com

**Resumo:** a tecnologia CMOS tem sido cada vez mais utilizada devido aos transistores MOS poderem ser fabricados em dimensões menores [1]. Sabendo que em qualquer tecnologia de fabricação de circuitos digitais, o elemento básico é o inversor, este foi o dispositivo escolhido para este estudo. Neste trabalho foi estudado o comportamento do inversor CMOS operando em diferentes temperaturas através de medidas experimentais e de simulações de circuitos SPICES para melhor compreender seu comportamento.

# 1. Introdução

Com a evolução tecnológica e o aumento da densidade de integração dos dispositivos, o aumento da temperatura de operação dos circuitos integrados tornasse crítica. O estudo do comportamento dos dispositivos em altas temperaturas é de fundamental importância para a compreensão de circuitos mais complexos.

É sabido que a variação da temperatura impacta no cálculo do potencial de Fermi, na variação da concentração intrínseca de portadores  $n_i$ , e consequentemente no valor da tensão de limiar  $(V_T)$  [2].

Outro parâmetro importante que deve ser considerado é a variação da mobilidade dos portadores que tem essencial importância nos circuitos fabricados em tecnologia [3].

## 2. Metodologia

Foram medidos 6 CIs HD74HC04P, da fabricante Renesas, sendo que cada CI contém seis inversores CMOS em seu interior. Uma estufa calibrada foi utilizada para realização das medidas em diferentes temperaturas. O range de temperatura adotado foi de 25°C até 95°C. A freqüência adotada foi de 500kHZ.

Através das equações (1) e (2) foi possível calcular a variação da tensão de limiar  $(V_T)$  e da mobilidade  $(\mu)$  de ambos os transistores.

$$\phi_F = \frac{k \cdot T}{q} \ln \frac{N_A}{n_i} \tag{1}$$

onde  $\phi_F$  é o potencial de Fermi, T a temperatura, k a constante de *Boltzmann*, q a carga do elétron,  $N_A$  a concentração de impurezas aceitadoras do semicondutor tipo P e  $n_i$  a concentração intrínseca de portadores de Si.

$$V_T = \frac{q \cdot N_a \cdot d_{m\acute{a}x}}{C_{OX}} + 2\phi_F - \frac{Q_{SS}}{C_{OX}} + \phi_{MS}$$

(2)

onde  $d_{m\acute{a}x}$  é a largura máxima da região de depleção,  $C_{OX}$  a capacitância do óxido de porta,  $\phi_{MS}$  a função trabalho do metal e semicondutor e  $Q_{SS}$  a carga do óxido.

Os principais parâmetros alterados na simulação devido a mudança de temperatura foram a mobilidade do nMOS e a tensão de limiar de ambos os transistores.

#### 3. Resultados

A variação da tensão de limiar é aproximadamente 0,83mV/°C para os dois transistores.

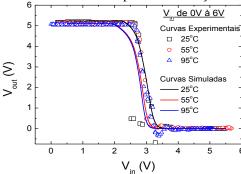

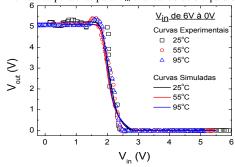

A figura 1 mostra tanto as curvas de transferência experimental como simulada para diferentes temperaturas quando a tensão de entrada passa de nível lógico baixo para alto. A figura

2 apresenta o mesmo tipo de análise, porém considerando a mudança da tensão de entrada de nível lógico alto para baixo. As duas análises não foram apresentadas em um único gráfico, pois como estes inversores apresentam uma histerese entre as excursões de sinal, a análise da variação da temperatura ficaria prejudicada. Esta histerese deve-se à diferença entre as tensões de limiar dos transistores p e nMOS.

A redução da tensão de limiar do transistor nMOS com o aumento da temperatura é o fator predominante para a pequena redução da tensão de inversão apresentada na figural. O comportamento dos inversores no retorno da tensão de entrada para 0V mostrou-se menos susceptível a esta variação.

Figura 1 – Curvas de transferência experimental e simulada para diferentes temperaturas para V<sub>in</sub> chaveando de 0V para 6V.

Figura 2 – Curvas de transferência experimental e simulada para diferentes temperaturas para  $V_{\rm in}$  chaveando de 6V para 0V.

### 4. Conclusões

A tensão de inversão na ida sofre uma alteração de 0,19V com o aumento de temperatura devido a variação da tensão de limiar do transistor nMOS, já na volta ela não é perceptível devido a tensão de limiar do transistor pMOS. Com o aumento da temperatura as mobilidades dos portadores e as tensões de limiares de ambos os transistores diminuem.

#### 5. Referências

- [1] Hausler, Ludwig. Tecnologia MOS. São Paulo: Nobel, 1986.

- [2] Martino, A. J. Pavanello, A. M. Verdonck, B. P. Caracterização Elétrica de Tecnologia e Dispositivos MOS. Thomson 2004.

- [3] Nikhil Satyala, Ron Pieper, Wudyalew Wondmagegn, "Simulation and transient analysis of organic/inorganic CMOS inverter circuit," ssst, pp.324-329, 2009 41st Southeastern Symposium on System Theory, 2009

<sup>&</sup>lt;sup>1</sup> Carolina de Fátima Garcez Sanavio, aluna de IC do Centro Universitário da FEI com bolsa institucional.